VDD Scaling (KN8421_FO2_LP2) (FO4 inverter delay is 51ps, 55ps, 61ps,... | Download Scientific Diagram

a) Evaluating normalized leakage and delay of a 20-stage FO4 inverter... | Download Scientific Diagram

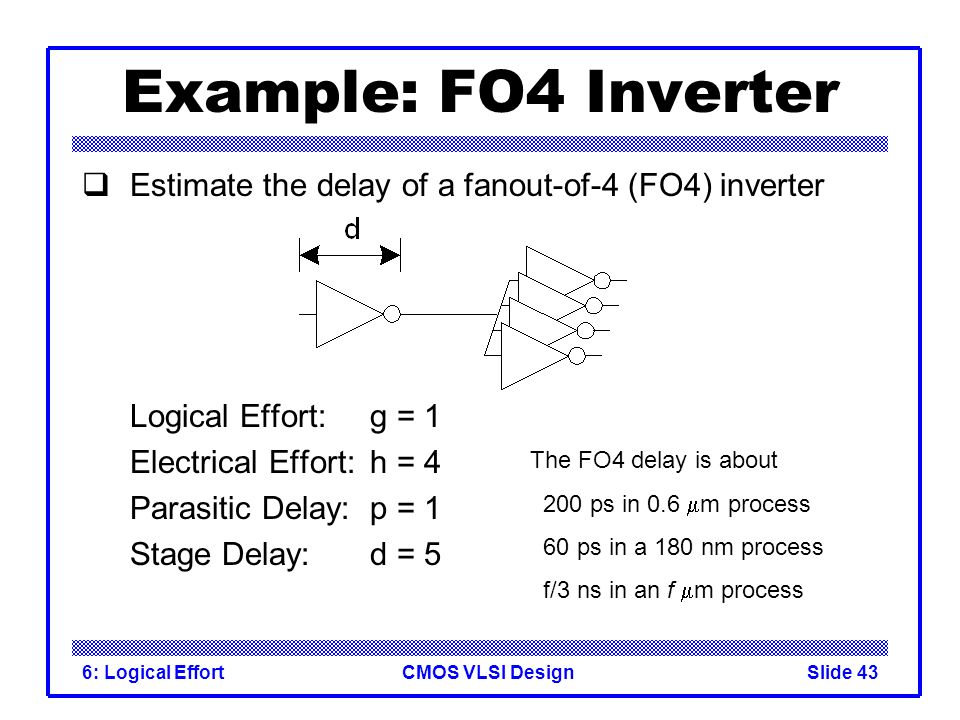

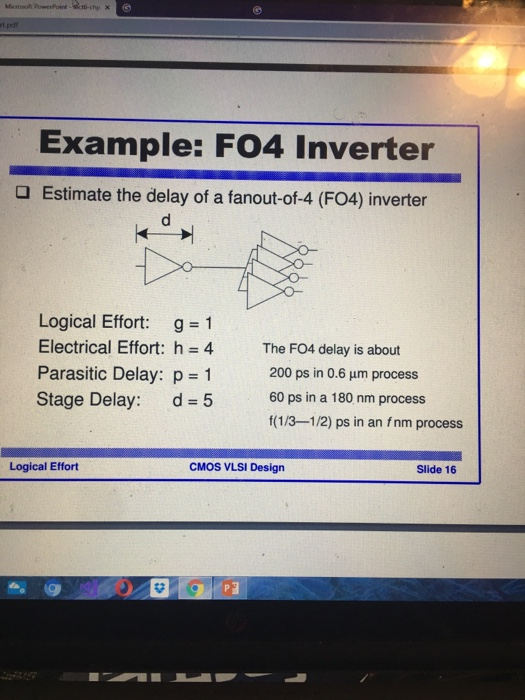

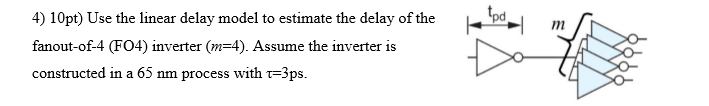

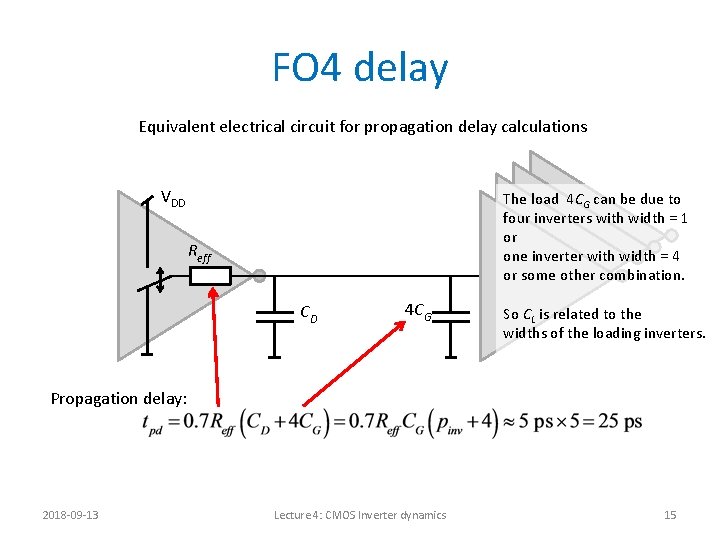

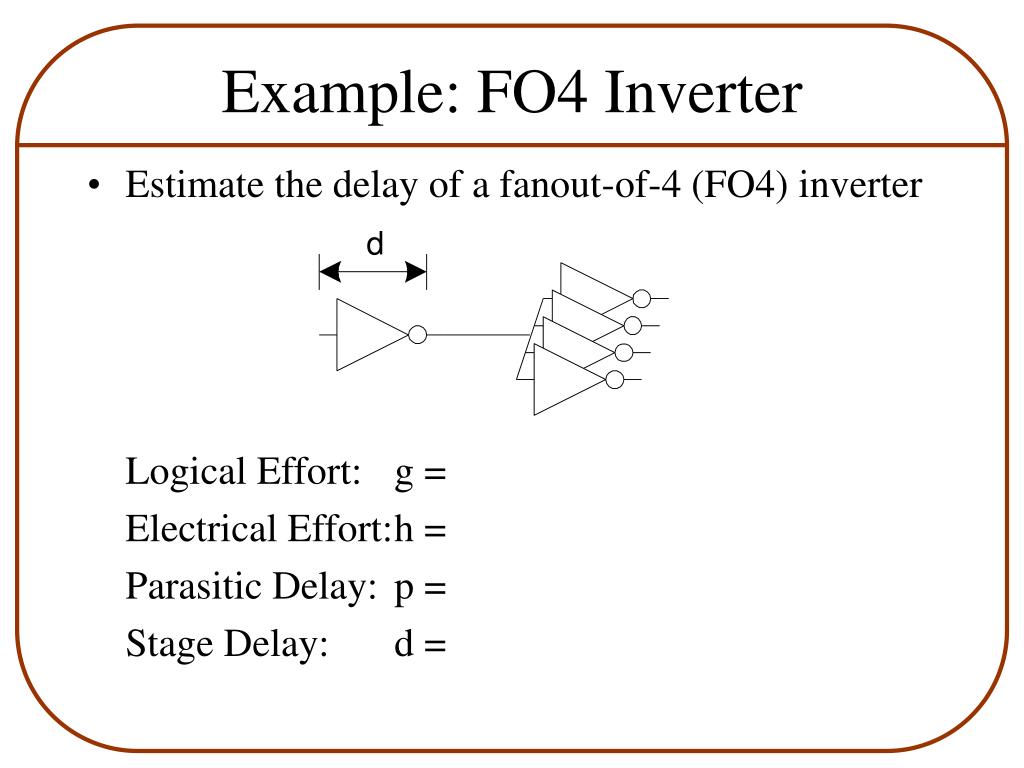

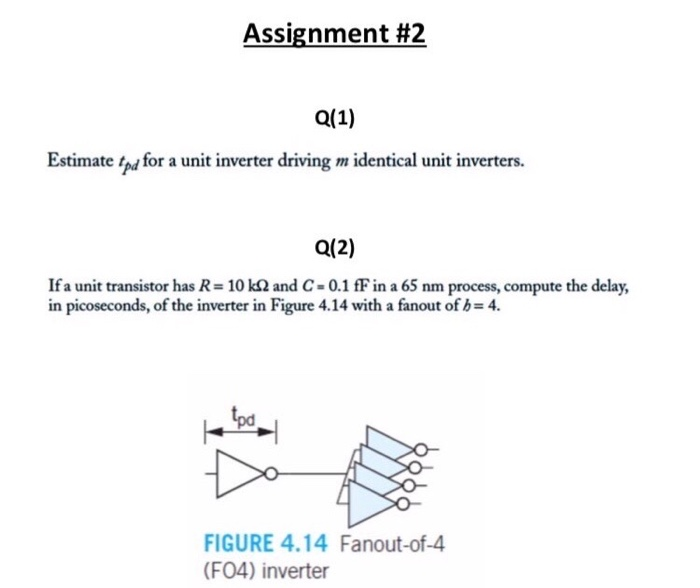

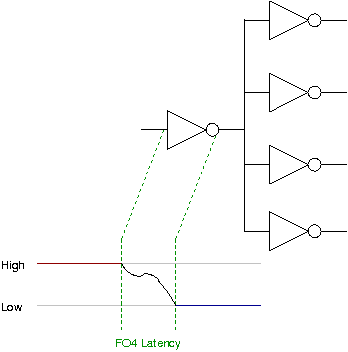

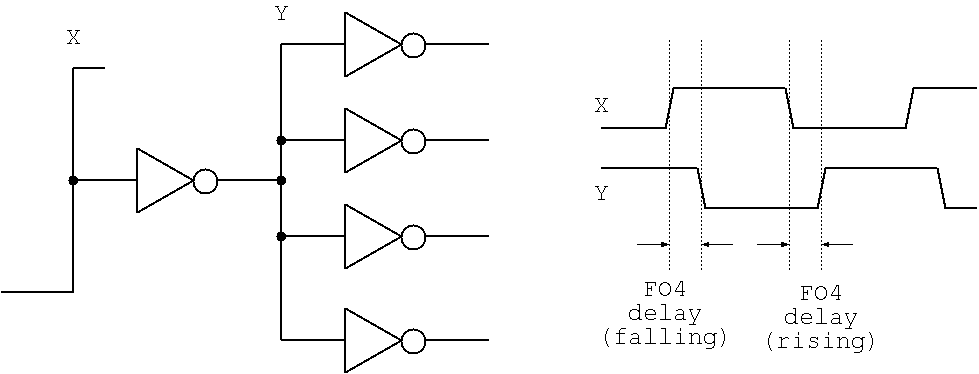

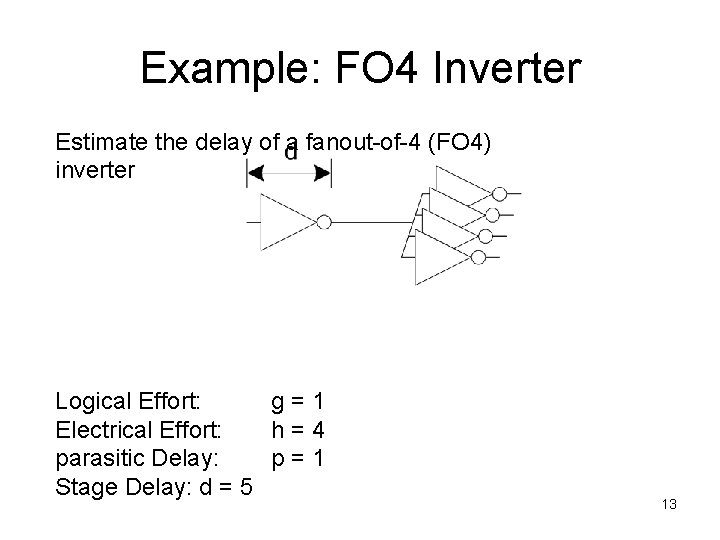

Gate Delay Model. Estimating Delays. Effort Delay. Gate Delay. Computing Logical Effort. Logical Effort - PDF Free Download

Evolution of I and total load capacitance of an FO4 inverter per width... | Download Scientific Diagram

![PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b29a6f1098b1b031f549dc65cbf77108ca9858d6/3-Figure3-1.png)

![The Stuff Dreams Are Made Of [Part 2] The Stuff Dreams Are Made Of [Part 2]](http://www.realworldtech.com/includes/images/articles/cmosintro2-fig4.gif?x56147)

![PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar PDF] The optimal logic depth per pipeline stage is 6 to 8 FO4 inverter delays | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b29a6f1098b1b031f549dc65cbf77108ca9858d6/3-Table1-1.png)

![The Stuff Dreams Are Made Of [Part 2] The Stuff Dreams Are Made Of [Part 2]](http://www.realworldtech.com/includes/images/articles/cmosintro2-fig3.gif?x56147)